4.4. Триггеры

Триггер

– это устройство с двумя устойчивыми состояниями, одно из которых – логический нуль, другое – логическая единица. Эти состояния триггера при бесперебойном питании и при отсутствии существенных помех и наводок могут сохраняться сколь угодно долго. Под действием управляющих сигналов триггер способен переключаться из одного состояния в другое. Основноеназначение триггера – хранение двоичной информации. Например, в персональных компьютерах на триггерах собрана кэш-память первого и второго уровней.

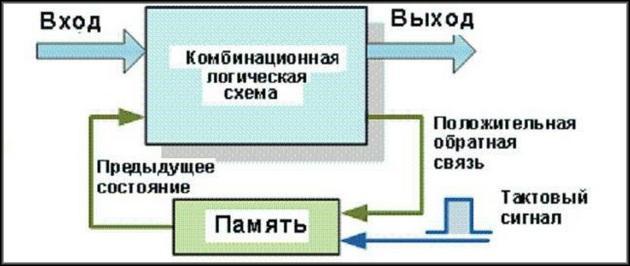

Триггер, в отличие от комбинационных схем, относится к новому виду цифровых устройств – цифровым автоматам

. Цифровые автоматы, кроме комбинационных схем, содержат элементы памяти. Если выходные сигналы цифрового автомата зависят как от входных сигналов, так и от состояния запоминающего устройства, то такие автоматы называют автоматами Мили. Если выходные сигналы определяются только состояниями запоминающего устройства, то получим автомат Мура.

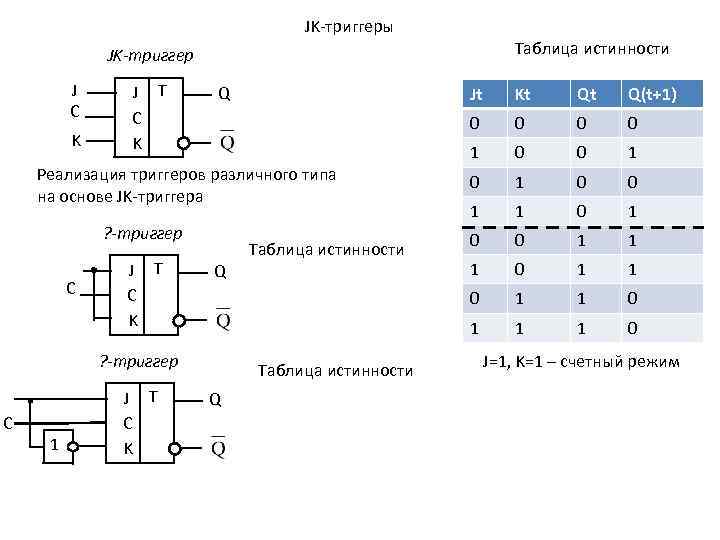

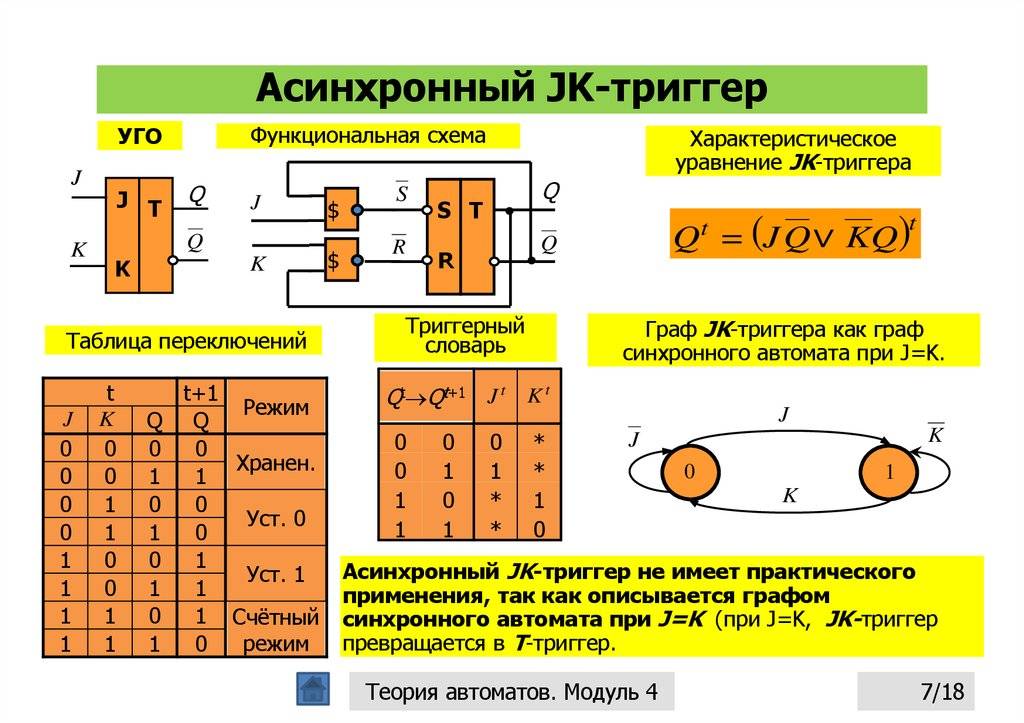

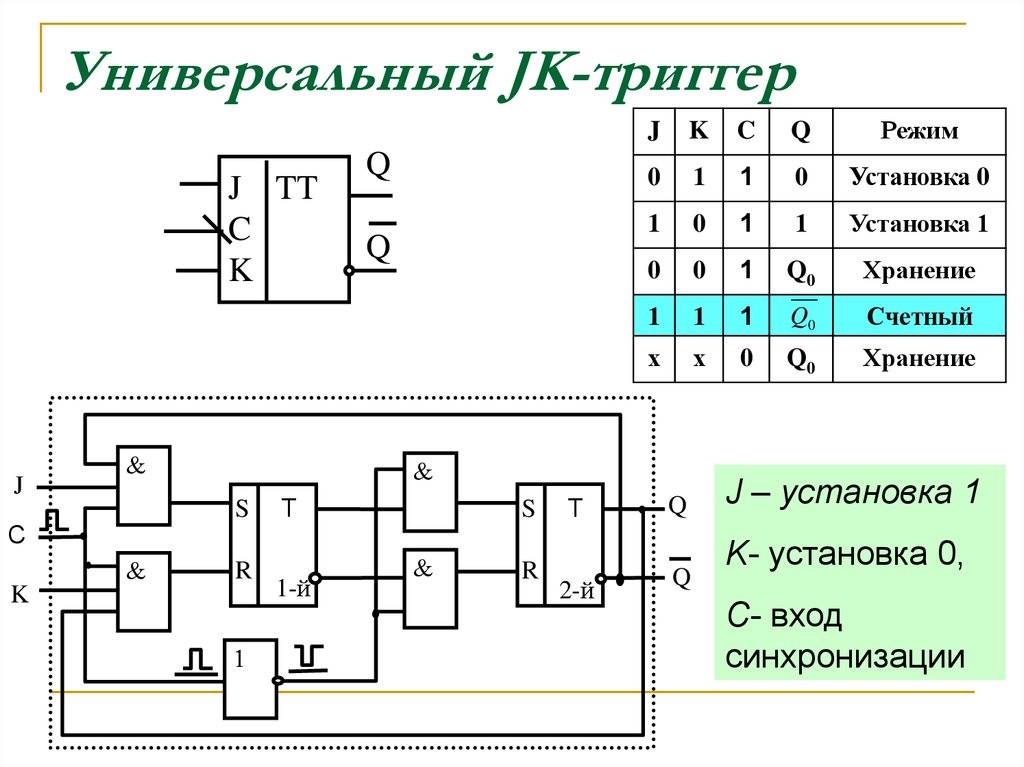

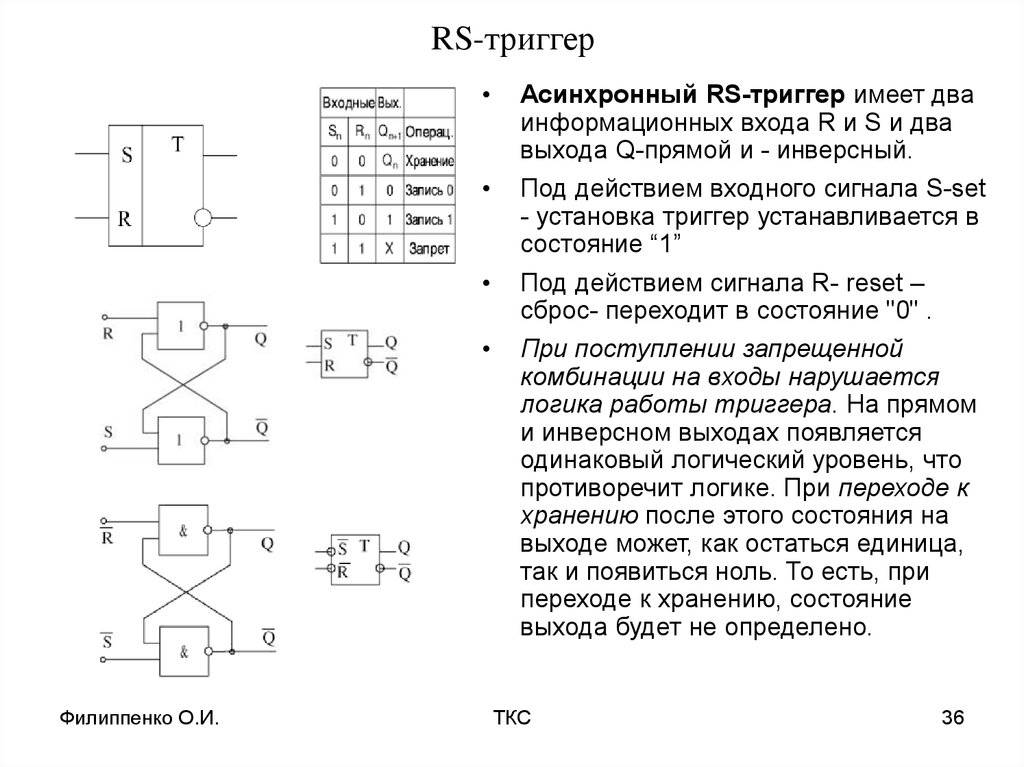

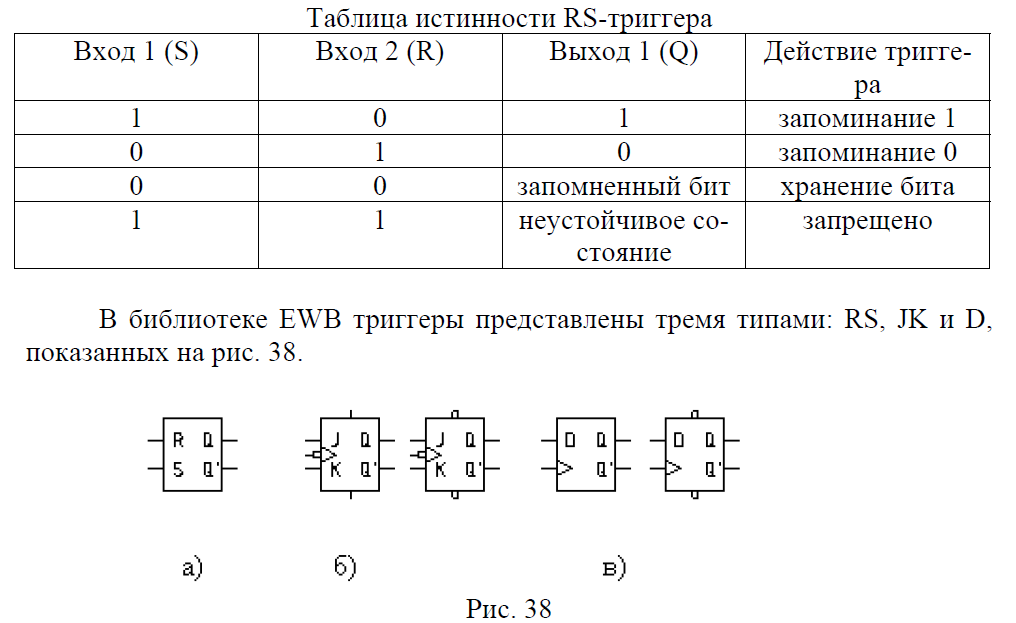

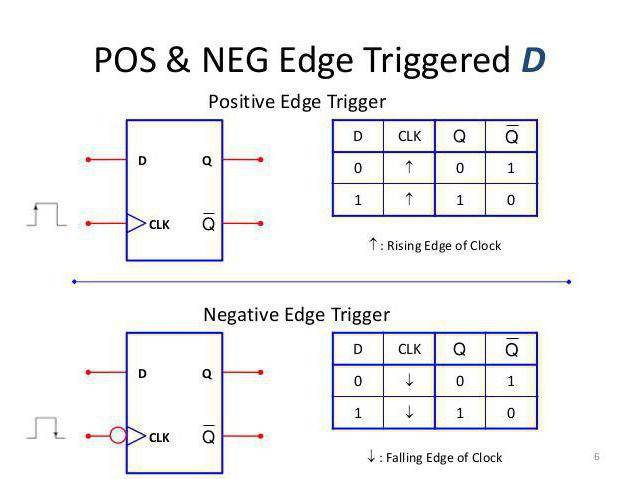

Различают несколько разновидностей триггеров: RS

-триггер,D -триггер,JK -триггер. Реже используютсяDV -триггер иТ -триггер. Если для изменения состояния триггера используется синхронизирующий сигнал, то триггер называетсясинхронным (синхронизируемым). Если синхронизирующие сигналы не используются, то триггер называетсяасинхронным .

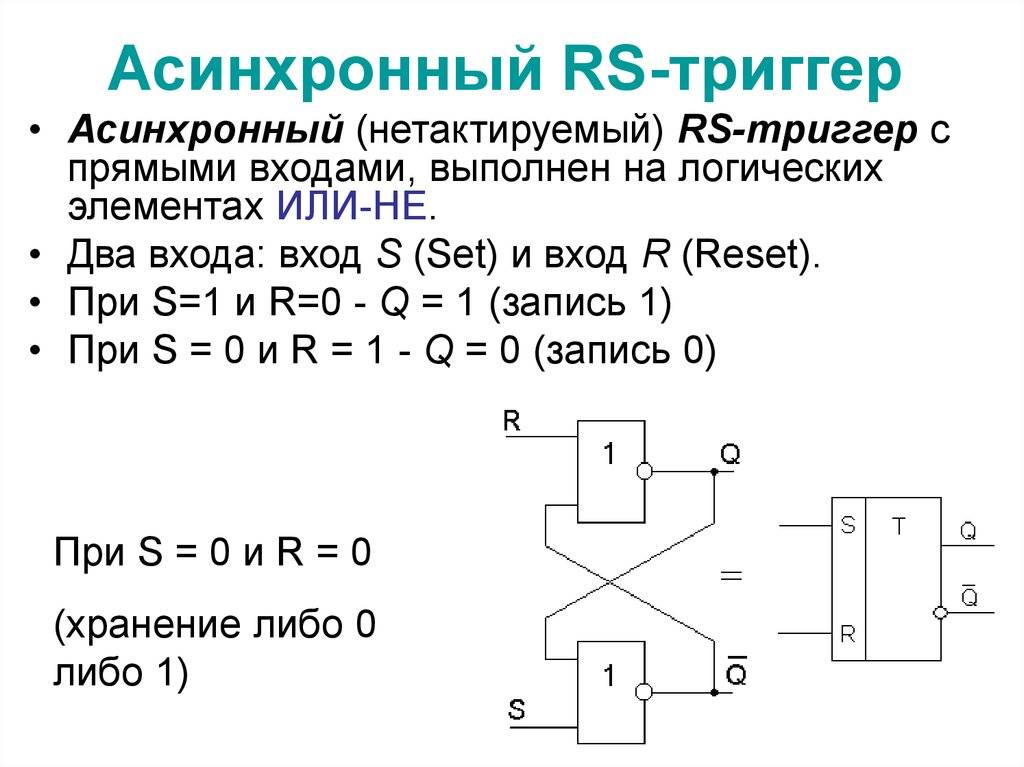

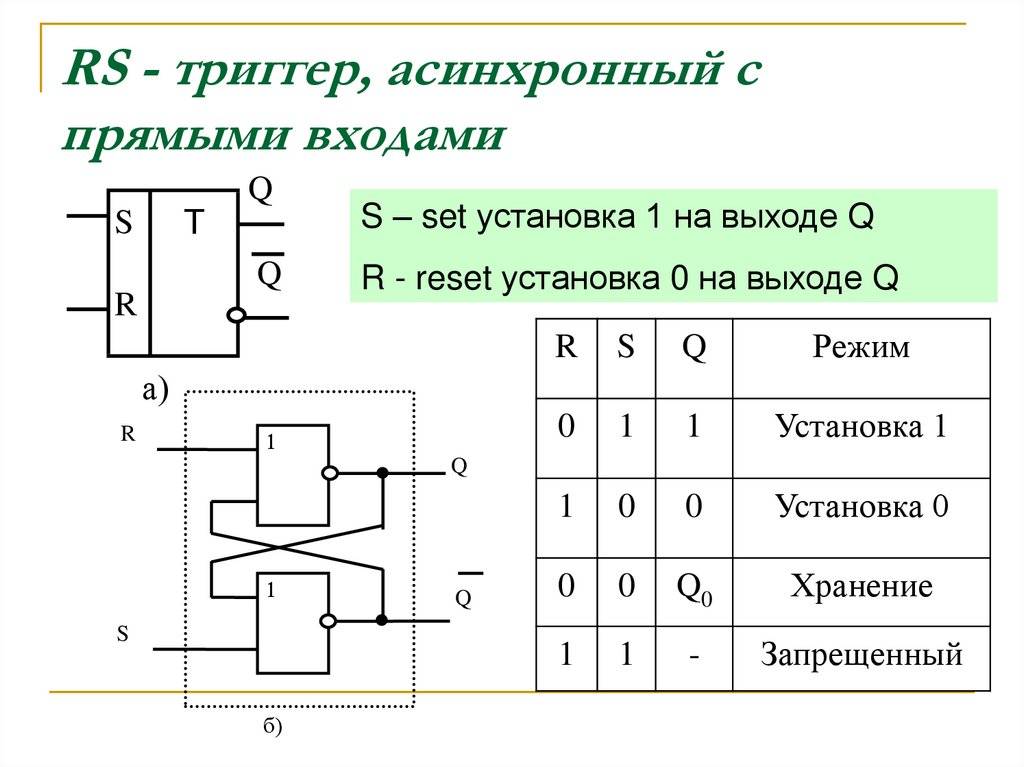

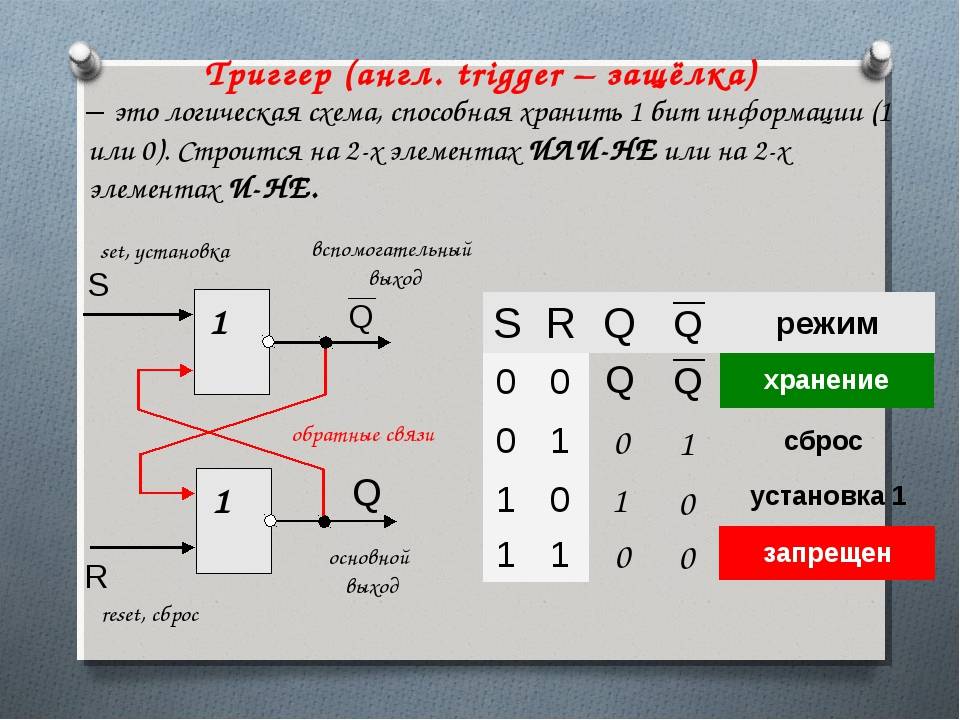

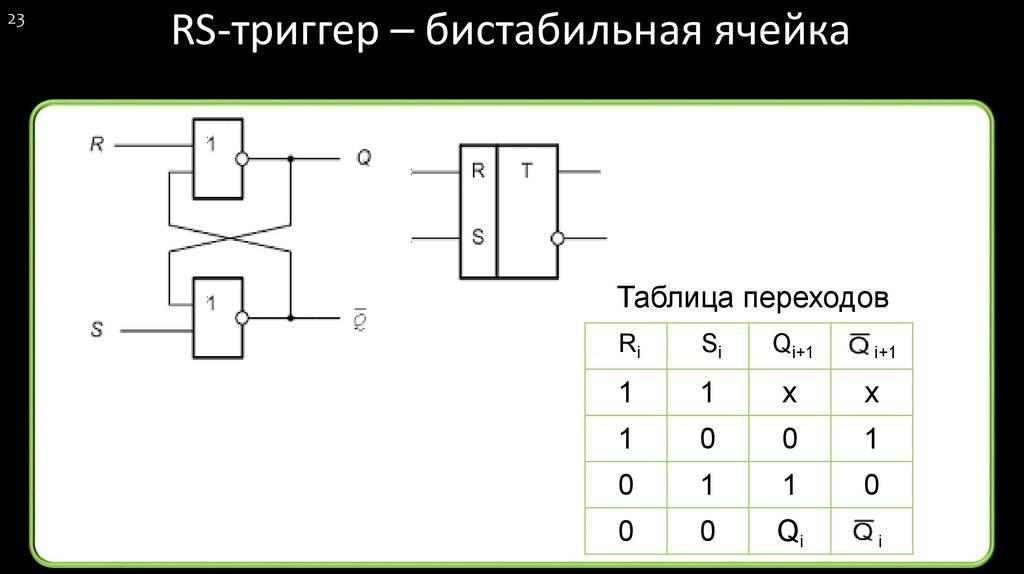

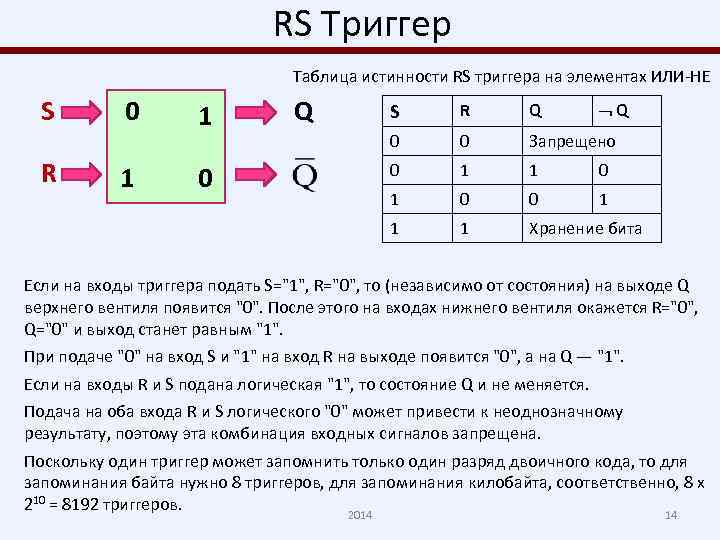

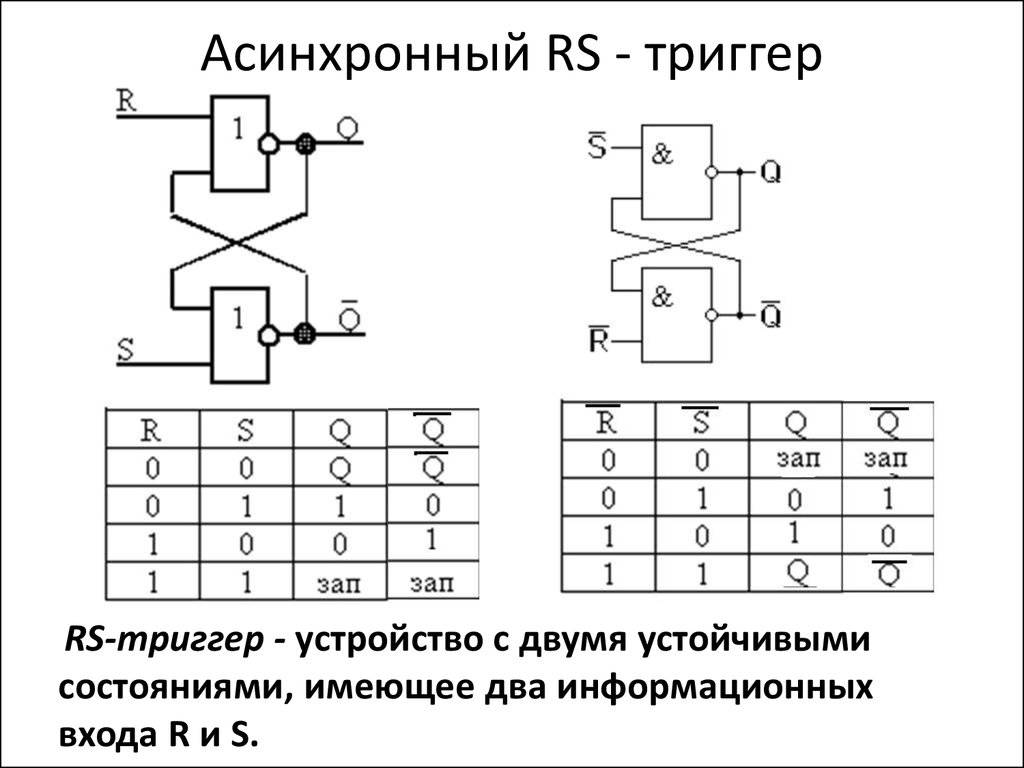

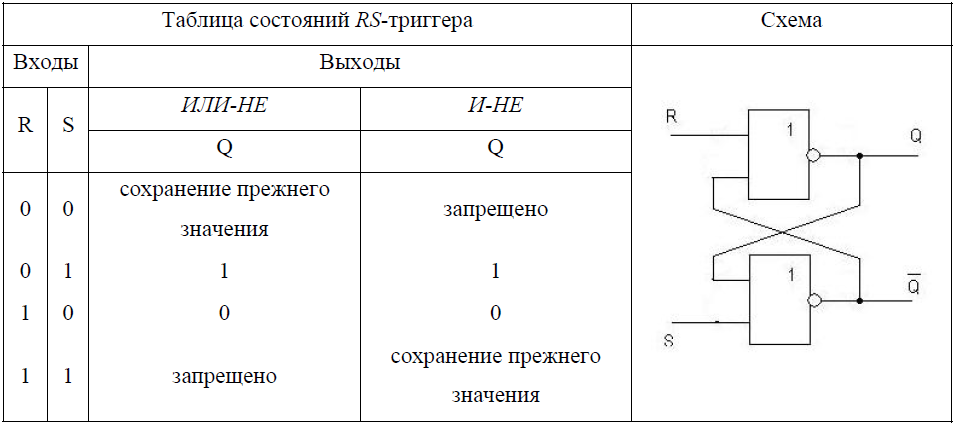

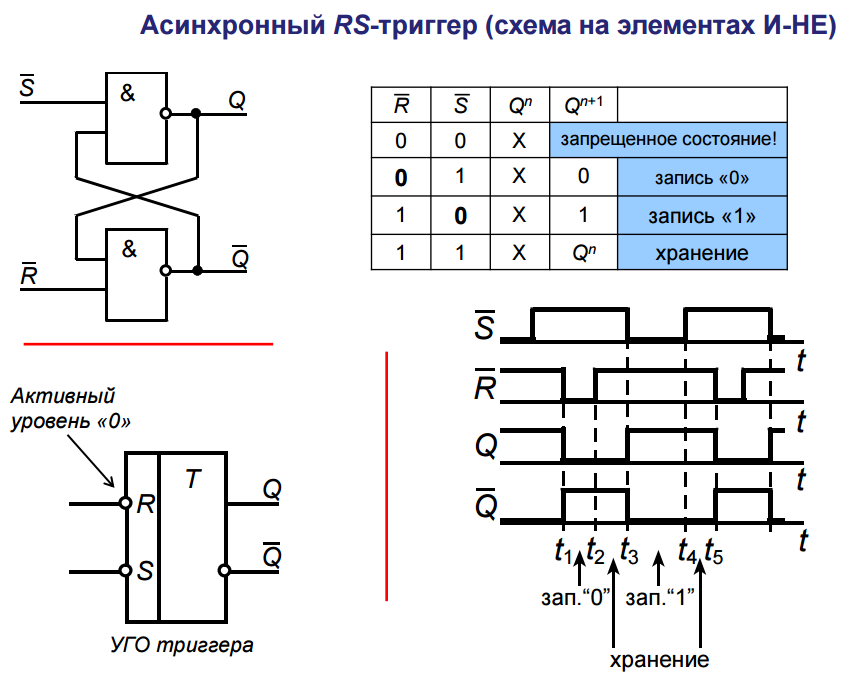

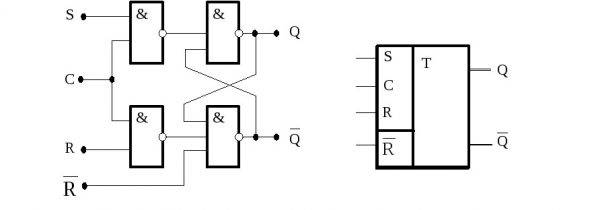

Например, в простейшем асинхронном RS- триггере

использованы схемы ИЛИ-НЕ (стрелка Пирса) с перекрестными обратными связями (рис. 4.21). Здесь использованы следующие обозначения:R – вход установки триггера в 0;S – вход установки триггера в 1;Q – прямой выход триггера; – вспомогательный (инверсный) выход триггера, сигнал на котором инвертирован относительно прямого выхода. Такие же обозначения используются для наименованиясигналов на соответствующих контактах триггера.

Рассмотрим работу RS

-триггера. Пусть в нулевой момент времени при нулевых сигналах на входахR иS на триггер подано напряжение питания. Однако на выходах триггера в этот момент времени оба выходных сигнала будут равны нулю:

Мгновенно эти сигналы увеличиться не могут, так как в реальных схемах всегда имеются паразитные емкости, а напряжение на конденсаторе скачкообразно измениться не может. Из свойств элемента ИЛИ-НЕ следует, что при нулевых сигналах на его входах напряжение на его выходе должно возрастать до значения логической единицы.

На практике из-за не идентичности двух элементов ИЛИ-НЕ на одном из выходов (Q или ) напряжение возрастает быстрее.

Пусть более быстро напряжение возрастает на выходе Q. Это напряжение поступает на второй логический элемент и начинает уменьшать напряжение на его выходе , устремляя его к нулю. В свою очередь, уменьшающееся напряжение на выходе , попадая на первый логический элемент, еще более ускоряет увеличение напряжения на выходе Q. Таким образом, благодаря положительной обратной связи быстро устанавливается единичное состояние триггера:

Q =

1;= 0.

Подавая на вход R

логическую единицу приS = 0 и используя свойства схемы ИЛИ-НЕ, получим:

Q

= 0; = 1.

Так производится операция установки триггера в нулевое состояние. Если после этого сигнал на входе R

сделать равным 0, то новое состояние триггера сохраняется.

При подаче единицы на вход S

и приR = 0 триггер устанавливается в единичное состояние:

Q

= 1.

Если R =S = 1, то на обоих выходах,Q и , возникают нули, что противоречит определению выходов триггера. Такая комбинация управляющих сигналовзапрещена (после этого работоспо собность триггера не теряется). Таблица состоянийRS —триггера приведена на рис. 4.22.

При хранении состояние триггера в данный момент времени определяется его состоянием в предыдущий момент времени:

где n

– номер временного отсчета. Условное обозначениеRS -триггера приведено на рис. 4.23.

Рассмотренный RS-

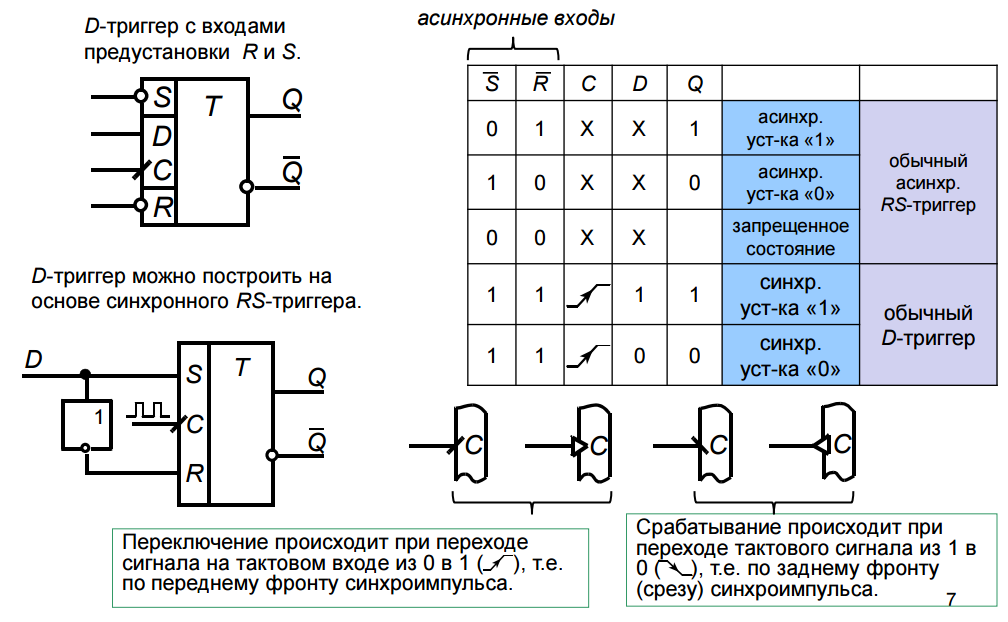

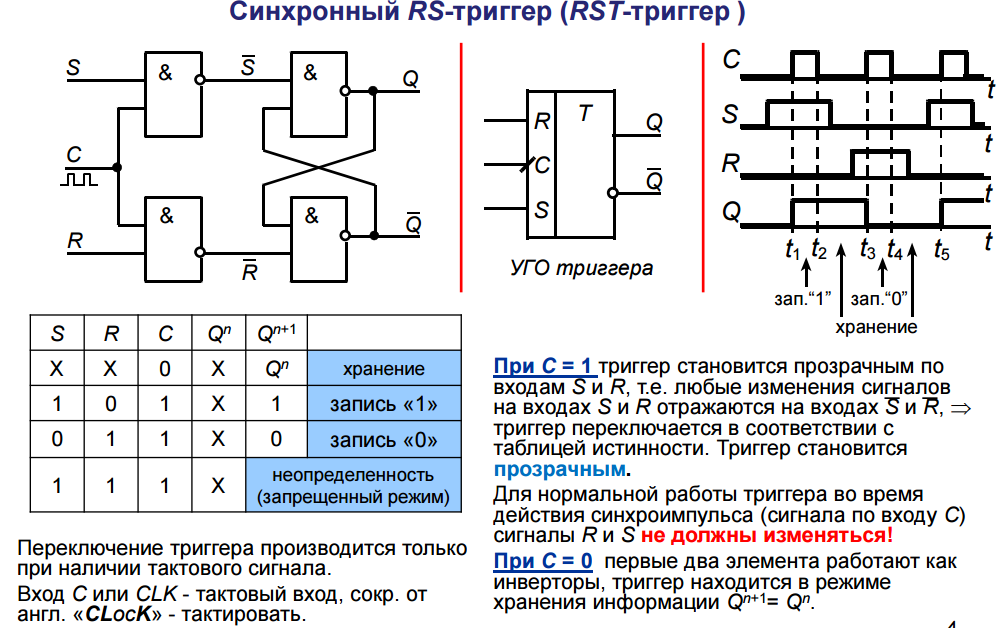

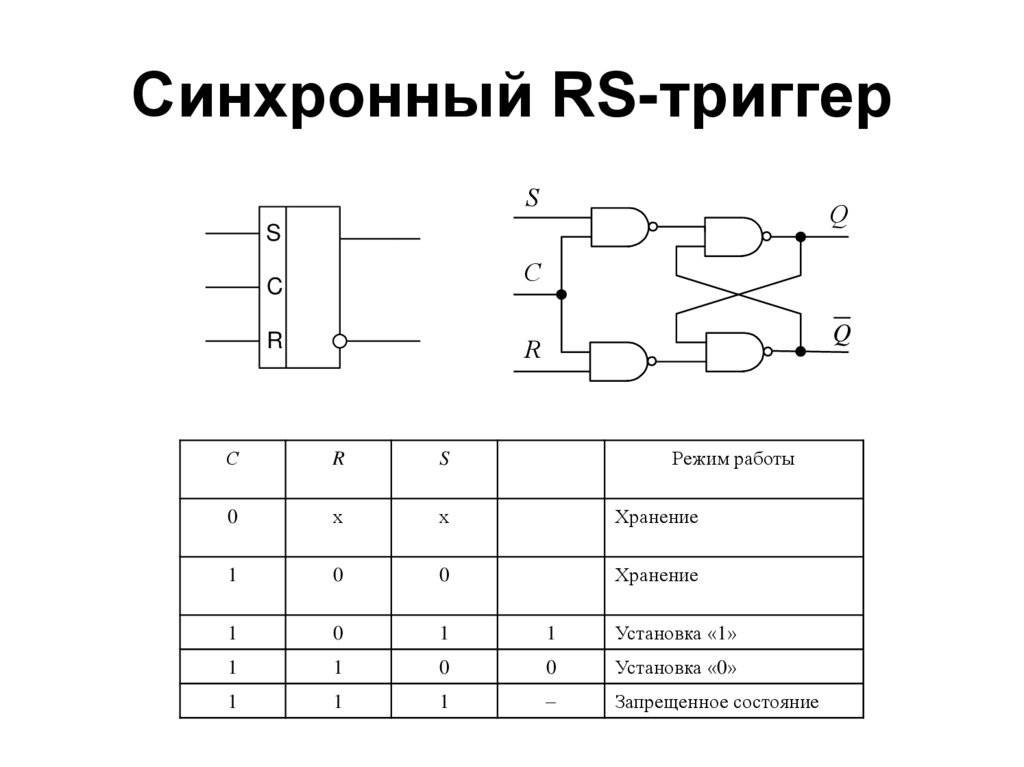

триггер при наличии помех часто работает ненадежно. Например, короткие импульсные помехи, попадающие наR — илиS -входы, могут изменить состояние триггера. Для повышения помехоустойчивости и для устранения «состязаний» используютсинхронныйRS-триггер, схема и условное обозначение которого приведены на рис. 4.24,а,б соответственно.

Состояние синхронного триггера может измениться только при установлении логической единицы на входе синхронизации С. В этом случае элементы И «открываются», и управляющие сигналы поступают на входы асинхронного триггера. Такая синхронизация называется статической

Принцип работы

Устаревшие элементы учёта затраченной электроэнергии

Во всех схемах имеет значение длительность рабочих реакций, которая определяет время записи (стирания). Определенное значение имеет помехоустойчивость. В следующих разделах рабочие процессы рассмотрены подробно.

Элементы с управлением по уровню

В этом варианте изменение состояния происходит только при высоком уровне синхронизирующего сигнала. При соответствующем положении устройство копирует изменения на входе с небольшой технологической задержкой. Если на С – ноль, реакция на выходе отсутствует.

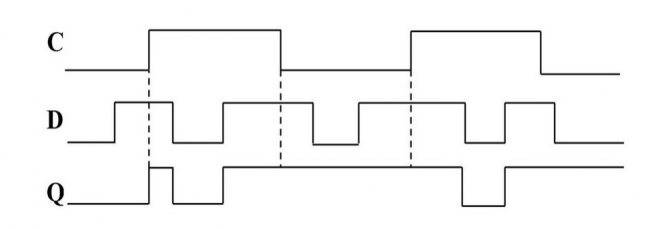

Временная диаграмма для управления триггером по уровню

Элементы с управлением по фронту

В соответствии с названием, здесь реализована схема управления по фронту (переднему и заднему). С помощью временной диаграммы можно рассмотреть рабочие циклы внимательно.

Изменение состояния при разных информационных (управляющих) сигналах

Допустим, что для управления выбран передний фронт. При С=0 состояние триггера не изменяется, вне зависимости от информационных сигналов, – одновременно с прохождением переднего фронта записывается аналогичное уровню D. В данном примере – единица. Следующие изменения происходят по такому же алгоритму.

Чтобы расширить базовую функциональность, устройство дополняют представленными выше сервисными входами (R и S). С их помощью состояние устанавливают произвольным образом (1 или 0) в любой нужный момент. Разумеется, для выполнения таких действий понадобятся дополнительные элементы управления.

К сведению. В этом варианте не имеет значения длительность управляющего сигнала. Для функционирования схемы его можно подать с применением инвертора в противофазе на два триггера Д типа, соединенные последовательно. Такое решение будет сопровождаться изменением состояния по заднему фронту (спаду).

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

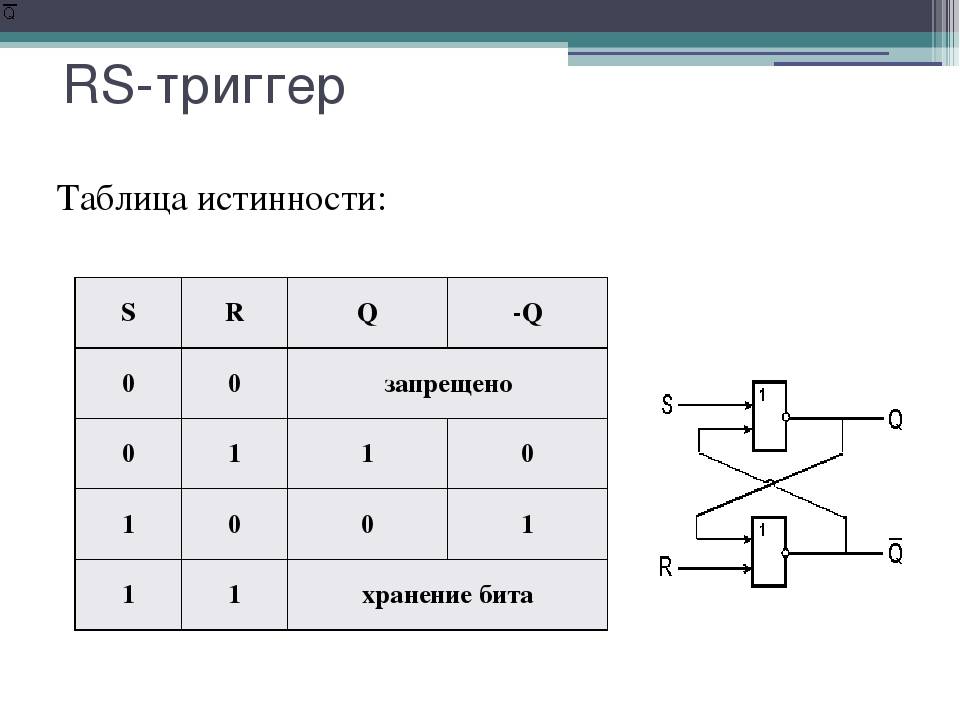

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

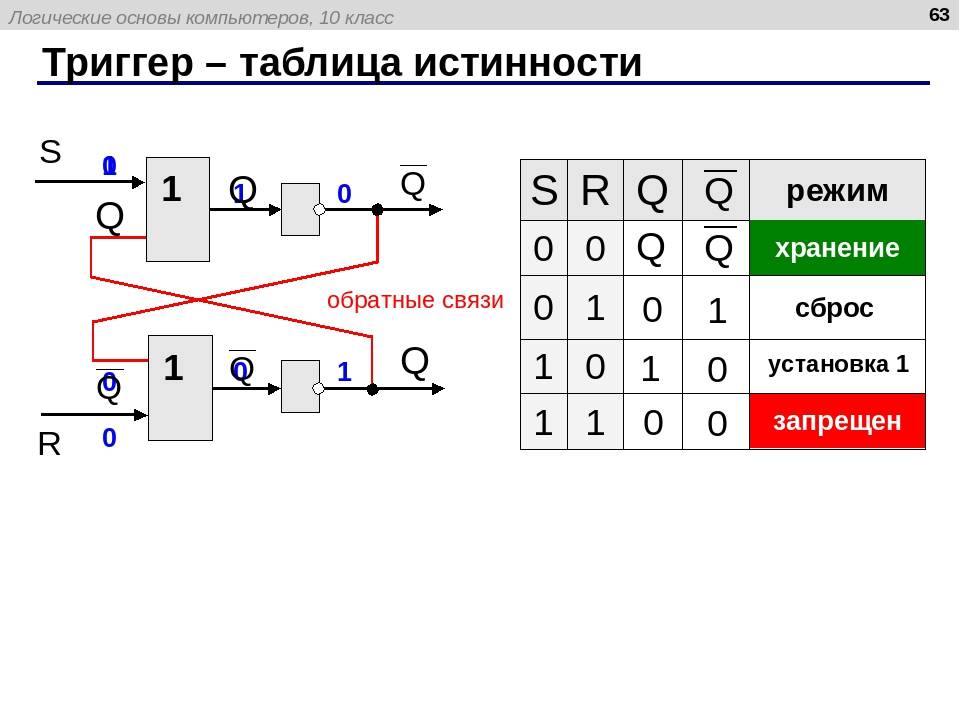

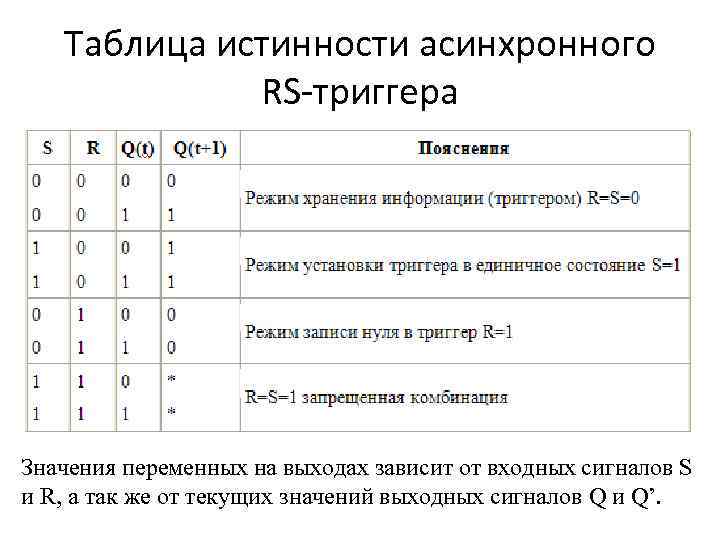

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

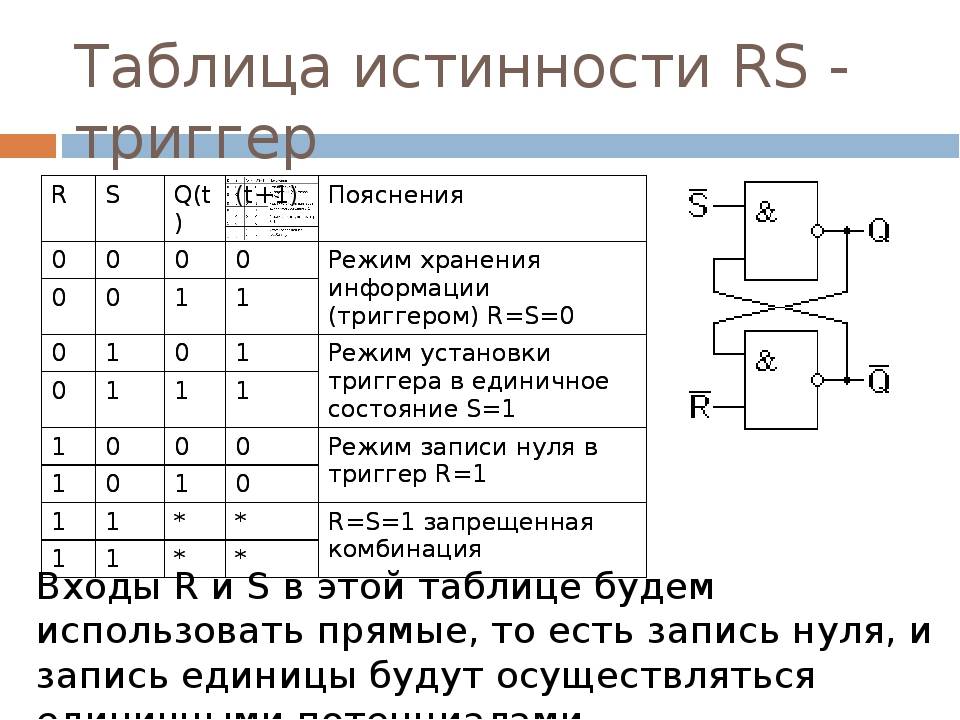

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

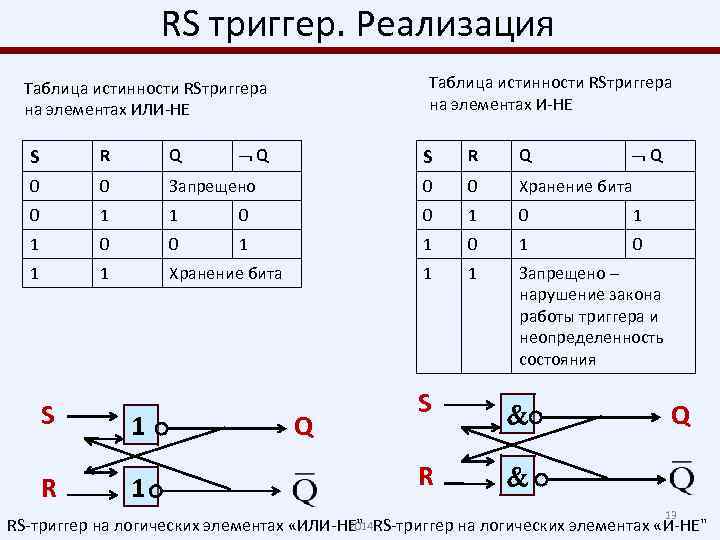

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

Триггеры. RS-триггеры. Асинхронный RS-триггер с инверсными входами

ТРИГГЕРЫ

Триггером называют устройство, имеющее два устойчивых состояния, способное под воздействием внешних сигналов переходить из одного состояния в другое. Свое состояние триггер может сохранять сколь угодно долго. Поэтому он может использоваться в качестве элемента памяти ёмкостью 1 бит.

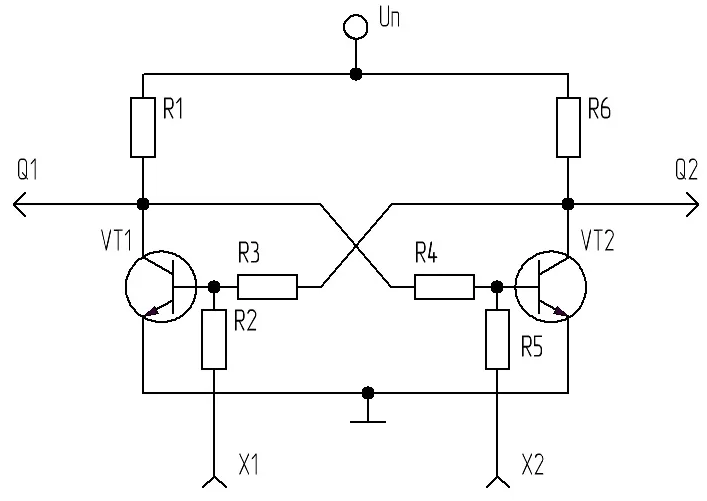

Схему с двумя состояниями можно легко построить на основе усилителя с глубокой положительной обратной связью аналогично автогенератору. Автогенераторы гармонических колебаний имеют узкополосную функцию передачи в петле обратной связи. В результате условие баланса фаз и амплитуд выполняется только на одной частоте, на которой и возникают колебания. В триггерах используют петлю с широкой полосой, начинающуюся с нулевой частоты. Это легко получить, если использовать усилитель постоянного тока или логический элемент.

Триггеры строятся на основе двух инвертирующих усилителей. Обобщенная схема представлена на рис.1.

Рис.1

Усилители образуют регенеративное кольцо из двух инверторов, охваченных глубокой положительной обратной связью. Поэтому переход из одного состояния в другое происходит лавинообразно за очень короткое время.

Триггер имеет два выхода: прямой Q

и инверсный. Состояние триггера определяют по значению сигнала на прямом выходеQ. Значения сигналов на прямом и инверсном выходах всегда противоположны.

Реальные логические элементы практически всегда обладают значительным усилением триггеры очень удобно строить на основе схем И-НЕ или ИЛИ-НЕ.

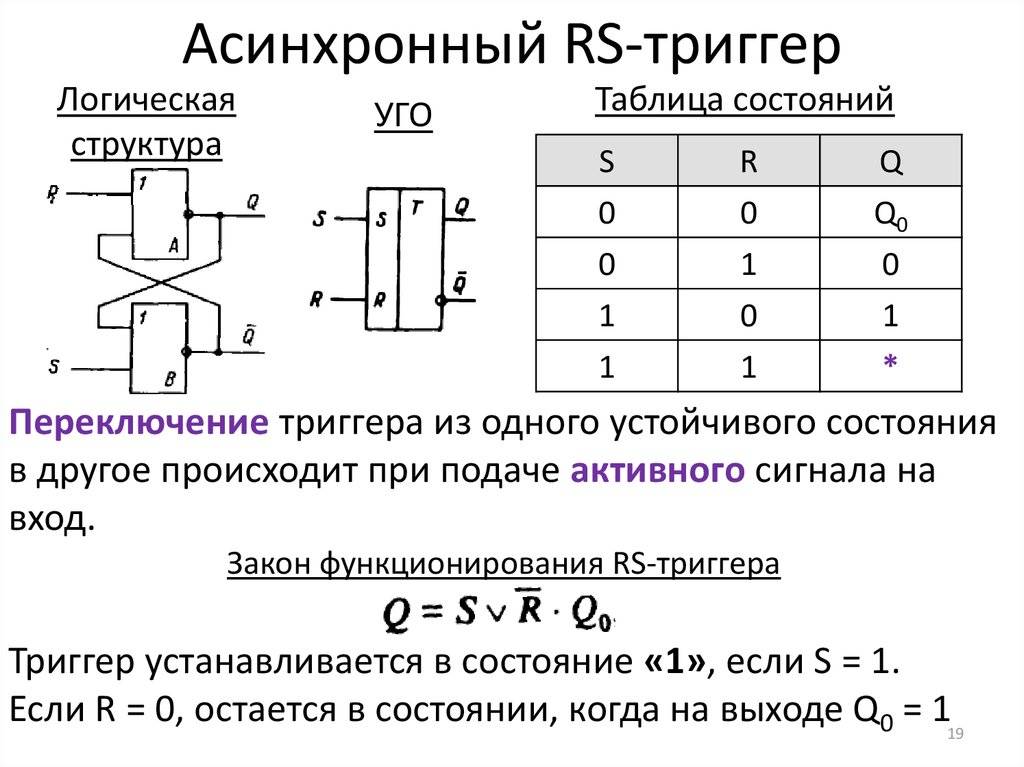

1.RS-триггеры ‘АсинхронныеRS-триггеры. В асинхронных триггерах срабатывание происходит непосредственно в момент изменения сигнала на информационных входах. АсинхронныеRS -триггеры являются наиболее простыми. В качестве самостоятельного устройства используются редко, но являются основой для построения более сложных систем.

RS

-триггер — это триггер с раздельной установкой состояний логического нуля и логической единицы. Он имеет два информационных входаS иR.. По входуS триггер устанавливается в состояниеQ =1( =0), по входуR— в состояниеQ =0(= 1). В зависимости от логической структуры асинхронныеRS -триггеры бывают с прямыми либо инверсными входами и могут строиться на двух логических элементах: 2ИЛИ-НЕ — триггер с прямыми входами; или на элементах 2И-НЕ — триггер с инверсными входами.

АсинхронныйRS-триггер с прямыми входами на логических элементах 2ИЛИ-НЕ представлен на рис. 2.

Рис.2.

Логические элементы ИЛИ-НЕ с инвертированием сигнала образуют петлю положительной обратной связи. При таком соединении логическая единица на выходе одного логического элемента (ЛЭ) поступает на вход другого ЛЭ и обеспечивает логический ноль (инвертирование) на его выходе. Логический ноль на выходе ЛЭ, поступая на вход другого, при инвертировании дает логическую 1. Таким образом, выходы Q

и всегда находятся в противоположных состояниях. Соединение элементов по данной схеме позволяет получить цепь с двумя устойчивыми состояниями.

Временные диаграммы, характеризующие работу асинхронного RS

-триггера с прямыми входами, показаны на рис. 3.

Рис.3

Для элементов ИЛИ-НЕ активным является высокий уровень — логическая 1, поэтому в режиме хранения данных на входы этого триггера подаются нулевые значения R

=S =0. Установка триггера в нужное состояние производится подачей на соответствующий вход активного уровня единицы. Одновременная подача единицы на оба входа (R и S) приводит к неопределенности. На обоих выходахQи появляются единицы, а после отключения входов (S=R=0) может установиться любое состояние

Физические реализации триггерных систем

В подзаголовке говорится о «триггерных системах» из-за того, что сами по себе эти устройства мало чего стоят. Но если необходимо сделать временную задержку перед выполнением или во время процедуры – их весьма сложно заменить. Также тот факт, что D-триггер может запросто длительное время работать без дополнительной настройки, позволяет его сделать очень ценным элементом любых схем, где необходима временная задержка. Для радиолюбителей они стали настоящим спасением при конструировании автоматических роботизированных станков, ведь эти элементы позволяют сделать временную задержку, необходимую для того, чтобы в рабочую область подать материал или деталь.

Синхронные и асинхронные триггеры: в чем разница?

https://www.syl.ru/article/210073/new_d-trigger-shema-i-printsip-rabotyi

Синхронные устройства имеют только логические (или по-другому – информационные) входы. Асинхронные механизмы срабатывают сразу, как только получили сигнал. Они не ждут, пока пройдёт временная задержка в тех элементах, которые образуют триггер. Асинхронный D-триггер не работает как устройство в обычном понимании. Благодаря этому он имеет один несомненный плюс: всегда, когда подаётся сигнал на вход, этот логический элемент сразу меняет значение выхода, а не ждёт определённой тактовой частоты. Для тех, кто умеет создавать близкие к идеальным схемы, триггеры будут весьма полезны.

Синхронные имеют не только информационные входы, у них также есть отдельный вход для подачи тактового сигнала. И именно к ним относится D-триггер. Он состоит из комбинационных схем (КС) и элементов памяти (ЭП). Из-за того что при наличии тактового сигнала вся работа ориентируется на один такт, триггеры и разделили на синхронные и асинхронные устройства. Но конструктивная разница на этом не исчерпывается. Так, именно благодаря тактовому сигналу, его воздействию, можно полностью исключать из внимания переходные процессы, что позволяет, в свою очередь, облегчить работу с электроникой. Именно поэтому синхронный D-триггер является более популярным и используемым на практике. Даже пример, который был приведён в начале статьи, подразумевал его использование.

Регистр — устройство, используемое для хранения n

-разрядных двоичных данных и выполнения преобразований над ними.

https://ru.wikipedia.org/wiki/%D0%A0%D0%B5%D0%B3%D0%B8%D1%81%D1%82%D1%80_(%D1%86%D0%B8%D1%84%D1%80%D0%BE%D0%B2%D0%B0%D1%8F_%D1%82%D0%B5%D1%85%D0%BD%D0%B8%D0%BA%D0%B0)

Регистр представляет собой упорядоченный набор триггеров, обычно D-, число n

которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное[уточнить ] цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Основой построения регистров являются: D-триггеры, RS-триггеры, JK-триггеры.

4-х разрядный сдвиговый регистр, преобразователь последовательного кода в параллельный и обратно

Параллельные и последовательные регистры

Всем доброго времени суток! В прошлом посте я писал про триггеры, а сегодня практически продолжение этой темы – регистры. Почему продолжение? Потому что регистры (англ. Register) представляют собой несколько триггеров соединённых между собой различными способами.

Вообще регистров бывает два основных вида:

- параллельный регистр;

- последовательный регистр или регистр сдвига.

В обозначениях микросхем для регистров выделено суффикс ИР, например, К555ИР9, К555ИР27, К1533ИР35.

Параллельный регистр

Схема соединения триггеров в параллельном регистре

В данном типе регистров триггеры соединены параллельно, то есть каждый внутренний триггер имеет свой вход D и свой выход Q, которые не зависят от других триггеров, а также вход С, который называется тактовым входом и для всех входящих в регистр триггеров он является общим. Параллельные регистры бывают двух типов:

- тактируемые регистры, которые срабатывают по фронту сигнала управления (вход С);

- стробируемые регистры, которые срабатывают по уровню входного сигнала (вход С);

Наибольшее распространение получили тактируемые параллельные регистры.

Cинхронные схемы

Бывает, требуется применять схемы с логическими элементами, работающими на основе изменения состояния при создании специальных условий, не зависящих от статуса входов. При этом в схему добавляется логический компонент И, имеющий 2 входа и соединенный с триггерными входами. Теперь входы R и S будут выполняться через терминал И, имеется также третий вход для тактовых импульсов. Изменение работы триггера заключается в том, что на Q̃ и Q состояние будет варьироваться из-за прохождения высокого тактового сигнала на входе, называемого «включить».

Синхронная схема RS триггера

- Когда тактовый сигнал равен 0, выходные значения элементов И идентичны, фиксируя выходные сигналы в последнем запомнившимся статусе;

- При тактовом импульсе, соответствующем единице, вся схема приобретает прозрачность и начинает работать как нормальный РС триггер. При этом оба входа воспринимают сигналы R и S.

Основным преимуществом тактового сигнала является то, что выход этого триггера можно синхронизировать со многими другими схемами и устройствами, которые используют одни и те же тактовые импульсы. Эта компоновка используется для базового расположения памяти, например, применяя различные логические состояния к диапазону из восьми триггеров, а затем посредством синхронного тактового импульса заставляя систему хранить байт данных.

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Будет интересно Что такое электрическое поле: объяснение простыми словам

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

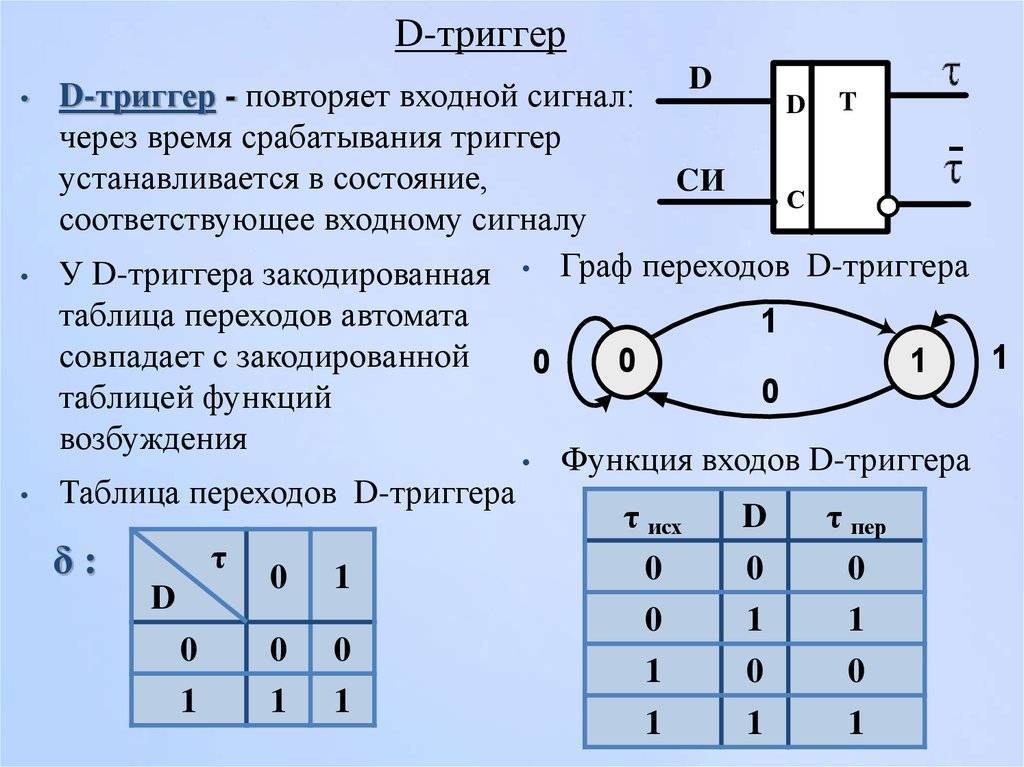

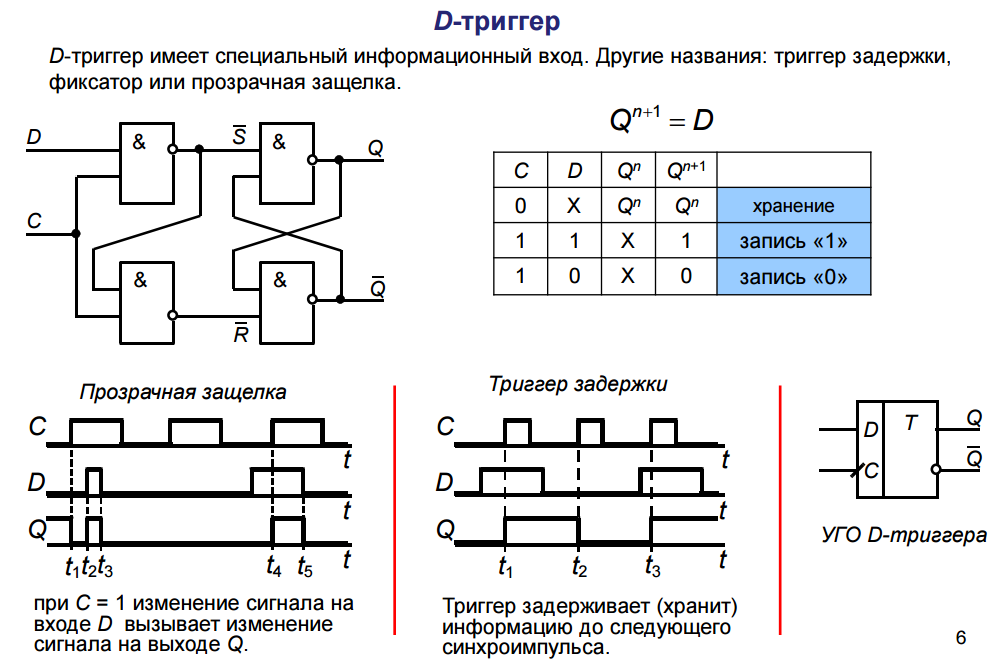

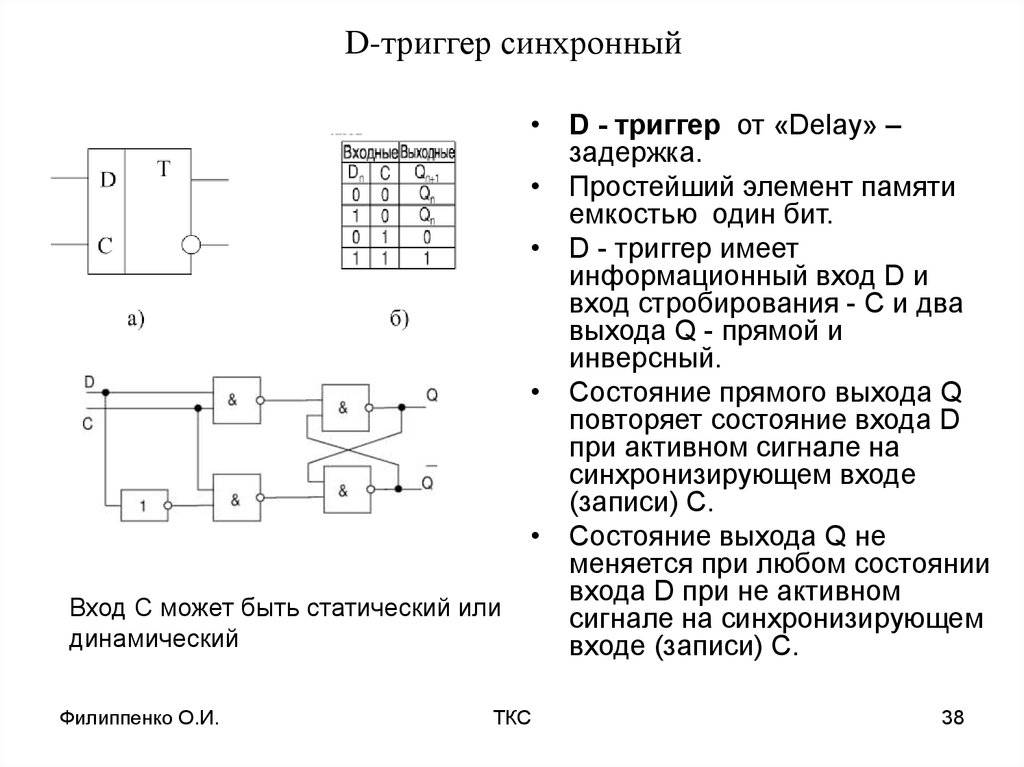

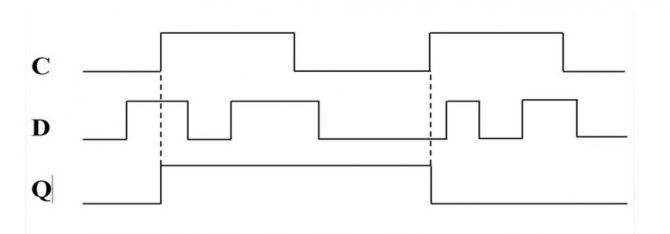

D триггеры, работающие по фронту.

Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время.

В идеале длительность фронта равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту не нужно предъявлять

требования к длительности тактового сигнала.

Триггер, запоминающий входную информацию по фронту, может быть построен из двух триггеров, работающих по потенциалу.

Сигнал синхронизации будем подавать на эти триггеры в противофазе. Схема такого триггера приведена на рисунке 15.

Рассмотрим работу схемы динамического триггера, приведенной на рисунке 15 подробнее. Для этого воспользуемся

временными диаграммами, показанными на рисунке 13. На этих временных диаграммах обозначение Q΄ соответствует

сигналу на выходе первого триггера. Так как на вход синхронизации второго триггера тактовый сигнал поступает через

инвертор, то когда первый триггер находится в режиме хранения, второй триггер пропускает сигнал на выход схемы. И

наоборот, когда первый триггер пропускает сигнал с входа схемы на свой выход, второй триггер находится в режиме

хранения.

Обратите внимание, что сигнал на выходе всей схемы в целом не зависит от сигнала на входе «D» схемы. Если первый

триггер пропускает сигнал данных со своего входа на выход, то второй триггер в это время находится в режиме хранения

и поддерживает на выходе предыдущее значение сигнала, то есть сигнал на выходе схемы тоже не может измениться.

В результате проведённого анализа временных диаграмм мы определили, что сигнал в схеме, приведенной на рисунке 15

запоминается только в момент изменения сигнала на синхронизирующем входе «C» с единичного потенциала на нулевой.

В результате проведённого анализа временных диаграмм мы определили, что сигнал в схеме, приведенной на рисунке 15

запоминается только в момент изменения сигнала на синхронизирующем входе «C» с единичного потенциала на нулевой.

Динамические D триггеры выпускаются в виде готовых микросхем или входят в виде готовых блоков в составе больших

интегральных схем, таких как базовый матричный кристалл (БМК) или программируемых логических интегральных схем (ПЛИС).

Условно-графическое обозначение D триггера, запоминающего информацию по фронту тактового сигнала,

приведено на рисунке 12.

То, что триггер запоминает входной сигнал по фронту, отображается на условно-графическом обозначении треугольником,

изображённым на выводе входа синхронизации. То, что внутри этого триггера находится два триггера, отображается в среднем

поле условно-графического изображения двойной буквой T.

Иногда при изображении динамического входа указывают, по какому фронту триггер (или триггеры) изменяет своё состояние.

В этом случае используется обозначение входа, как это показано на рисунке 18.

Рисунок 18. Обозначение динамических входов

На рисунке 18 а обозначен динамический вход, работающий по переднему (нарастающему) фронту сигнала. На рисунке 18 б

обозначен динамический вход, работающий по заднему (спадающему) фронту сигнала.

Промышленностью выпускаются готовые микросхемы, содержащие динамические триггеры. В качестве примера можно назвать

микросхему 1533ТМ2. В этой микросхеме содержится сразу два динамических триггера. Они изменяют своё состояние по

переднему фронту сигнала синхронизации.

Дата последнего обновления файла

09.03.2020

Принцип работы

Простой RS-триггер использует особый принцип работы, основанный на получении входных сигналов, которые в зависимости от поставленной задачи изменяют состояние выходов устройства. При входе сигнала на основной блок, на выходах происходит скачкообразное изменение напряжения, вследствие чего осуществляется управление поставленной задачей.

Логическое электронное устройство состоит из нескольких активных входных и выходных контактов. Рассмотрим эти контакты:

- Вход, использующийся для формирования выхода «Q». Его условное обозначение «R». На этом участке схемы происходит запись единицы.

- Вход, использующийся для сброса выхода «Q» обозначается буквой «S». На этом участке происходит запись нуля.

Далее рассмотрим, как работает простой RS-элемент.

Принцип работы простого RS-триггера невозможен без выходов. Они имеют такие обозначения:

- «Q» — является прямым выходом.

- «Q¯» — инверсный выход. В обозначение такого выхода добавлена черточка над буквой Q.

Самый первым был сделан триггер на транзисторах. Современные логические элементы сильно минимизированы, поэтому в основе всех таких устройств обязательно лежит микросхема. Такие устройства не подвержены воздействию помех, имеют низкий процент метастабильности, немного больше памяти и более широкие возможности для использования.

Транзисторные модели надежнее, но их основные недостатки: размер, наличие множества компонентов. Для увеличения памяти такие элементы подключаются параллельно в схему.